Hardware Hacking 101 - 입문, JTAG (Part1)

최근 하드웨어 해킹과 보안은 사이버 시큐리티의 새로운 화두가 되어 가고 있습니다. 하루 하루 쏟아져 나오는 많은 IoT 디바이스, 그리고 기존에 오랫동안 존재해 왔던 레거시 디바이스들의 보안 취약점들은 새로운 보안 위협으로 떠오르고 있습니다.

이 아티클을 통해서 하드웨어 해킹에 입문하기 위해서, 특히 하드웨어에 대해서 기본적인 분석을 수행하고, 펌웨어를 추출할 수 있는 여러 도구와 방법론에 대해서 논의해 보겠습니다.

하드웨어 해킹의 목적

하드웨어 해킹은 다음과 같은 여러 목적을 위해서 사용될 수 있습니다.

- Finding Vulnerabilities: 취약점 찾기

- Forensic Analysis: 수사적인 목적을 위한 포렌직 분석

- Modding: 기존 디바이스에 대한 업그레이드 내지는 펌웨어 변조를 통한 성능 향상이나 임플란트 백도어 설치

- Just for fun: 재미

Entry Point

기본적으로 하드웨어에 대해서 접근 권한, 특히 펌웨어에 대한 제어권을 확보하기 위해서는 크게 다음과 같은 4가지의 엔트리 포인트가 존재합니다.

- UART (Universal Asynchronous Receiver/Transmitter)

- JTAG (Joint Test Action Group)

- Storage: NAND Flash, ROM Flash, etc

- Bus: Accessing and hijacking PCB circuits

JTAG

JTAG은 원래 칩을 개발할 때에 핀 사이의 연결 상태를 체크하기 위한 장치(In-Circuit Testing)로서 개발 되었습니다. 특히, 지금처럼 PCB와 자동적인 납땜 기술의 에러율이 높았던 시기에 PCB 보드가 제대로 조립 되었는지 체크할 방법들이 필요했습니다. JTAG은 초기에 그러한 작업을 수행하기 위한 방법으로 사용되었습니다.

하지만, JTAG에 커넥션 테스트 이외에 칩 내부분의 여러 기능을 테스트하고, 데이타를 제어하고 디버깅하기 위한 여러 추가 기능들이 도입 되면서, 칩과 기판을 테스트하기 위한 표준 방법으로 거듭 나게 되었습니다.

다음은 JTAG에서 일반적으로 사용되는 여러 핀들에 대한 설명입니다. 이러한 핀들에 대해서 접근이 가능하면 JTAG 기능에 억세스 가능하다고 말할 수 있습니다.

| Name | Function | Description | State | |

|---|---|---|---|---|

| TCK (Test Clock) | Synchronizes the internal state machine operations | |||

| TMS (Test Mode Select) | Determines what action JTAG takes | Sampled at the rising edge of TCK to determine the next state | ||

| TDI (Test Data In) | Feeds data into the chip | The data shifted into the device’s test or programming logic. | It is sampled at the rising edge of TCK when the internal state machine is in the correct state. | |

| TDO (Test Data Out) | The pin that data comes out of the chip | The data shifted out of the device’s test or programming logic. | It is read on the falling edge of TCK when the internal state machine is in the correct state. | |

| TRST (Test Reset) | Reset JTAG to a know good state | An optional pin. Reset the TAP controller’s state machine |

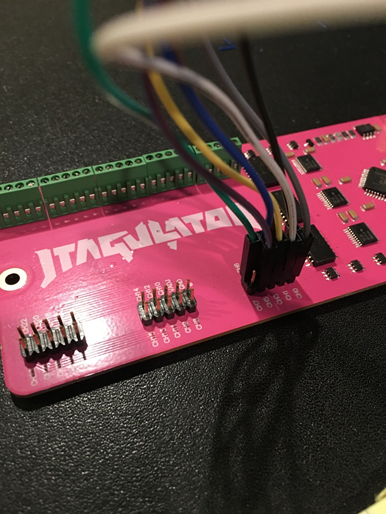

JTAGulator – automation with finding entry point

JTAGulator는 JTAG 핀들을 자동으로 찾아 줄수 도구입니다. 모두 15개의 핀에 대해서 JTAG의 핀들을 조합해서 찾아 줍니다.

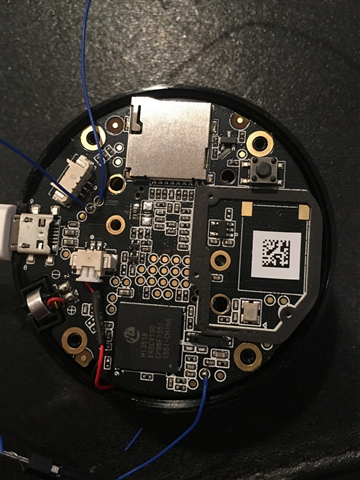

JTAGulator는 대상 기판에 가능한 JTAG 핀의 개수가 제한적일 때에 유용한 도구입니다. 예를 들어 다음 드랍캠의 내부에는 실질적으로 몇개 되지 않는 핀들만이 노출 되어 있으며, 그 중 일부분은 JTAG이나 UART에 억세스 가능한 핀일 가능성이 높습니다. JTAGulator는 JTAG 뿐만 아니라 UART 핀들도 휴리스틱하게 찾아 줍니다.

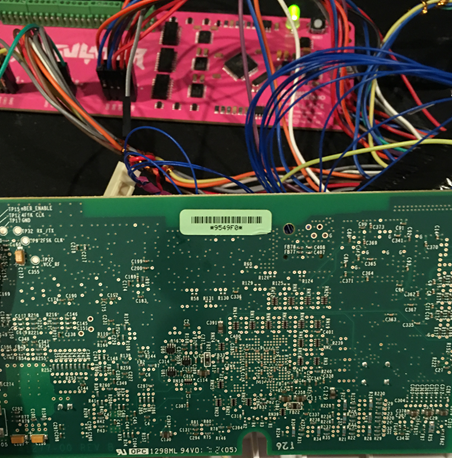

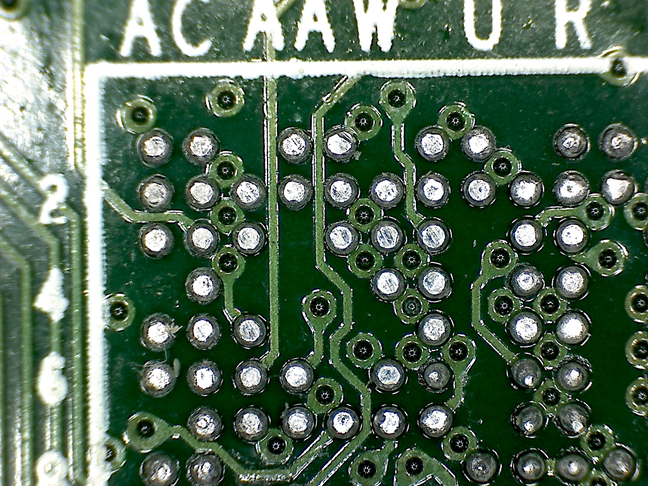

다음은 일반적인 임베디드 디바이스의 기판을 보여주는 사진입니다.

이렇게 수많은 핀들이 노출 되어 있고, 어느 핀들이 JTAG 내지는 UART일지 가늠이 안되는 경우에 JTAGulator는 사실 그렇게 유용하지 않은 경우가 많습니다. 먼저 이 수 많은 핀들 중에 JTAG 핀들에 가까운 핀들을 찾아 내든지, 아니면 아예 새로운 접근 방법이 필요합니다.

MCU (Microcontroller Unit)

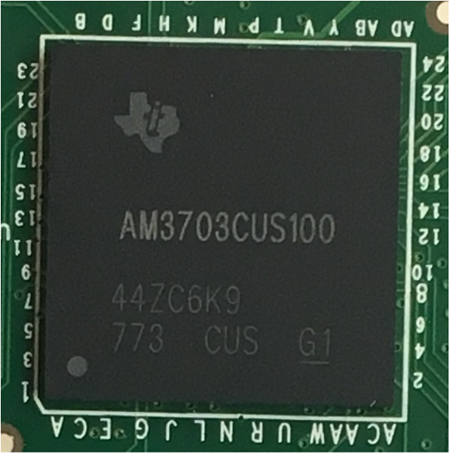

먼저 JTAG을 잘 찾아 내기 위해서는 MCU가 무엇인지 JTAG이 MCU에서 어떠한 개념인지에 대해서 다시 한번 정리해 볼 필요가 있습니다. 다음은 한 MCU를 확대한 모습니다. AM3703CUS100이라는 모델명이 보입니다. Digikey사의 정보에 따르면 이 MCU는 Texas Instrument사의 제품으로서 ARM® Cortex®-A8을 구현한 제품으로 보입니다.

MCU Specifications

이러한 정보를 바탕으로 JTAG 핀을 찾아 낼 수 있습니다. JTAG 핀은 실제로 MCU의 핀들로 정의 되어 있기 때문에, 그 핀들과 연결된 노출된 핀들을 찾으면 JTAG 핀들을 확정할 수 있습니다.

스펙 문서 검색 결과 다음과 같은 문서를 쉽게 구할 수 있습니다. 대부분의 양산용 전자제품과 IoT 디바이스의 경우 범용칩을 사용하므로 이러한 스펙 문서를 구하는데에 있어서 큰 문제는 존재하지 않습니다.

Pin layout

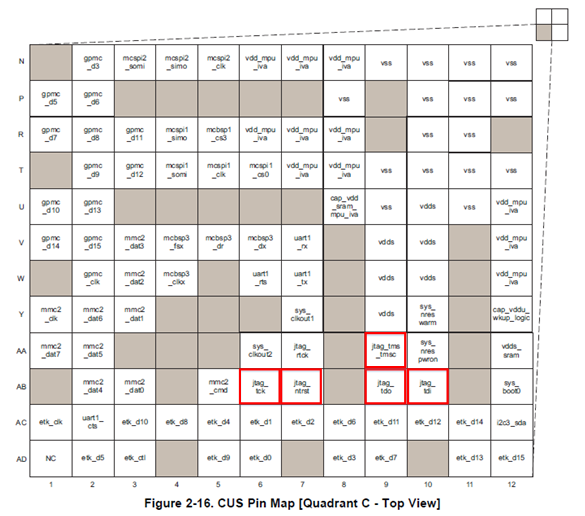

스펙 문서를 구한 다음의 과정은 MCU의 핀 layout을 알아 내는 것입니다. 대부분의 MCU 문서에는 다음과 같은 물리적 규격과 핀의 위치를 규정한 부분이 있습니다. A ~ AD 까지의 행을 규정하고 있고, 1 ~ 24의 숫자는 열을 규정하고 있습니다. 두가지 좌표를 사용하여 핀의 위치를 특정할 수 있습니다.

스펙 문서에는 각 해당 핀들의 역할과 기능을 정의해서 표기해 주는 경우가 대부분입니다. 다음과 같이 JTAG과 관련된 핀들을 특정하는 것이 가능합니다.

Desoldering

이렇게 MCU의 핀들에 대한 정보를 수집한 이후에는 실제로 이러한 핀 위치에 존재하는 납땜 부위와 거기에 연결되어 노출된 핀들을 찾는 과정이 필요합니다.

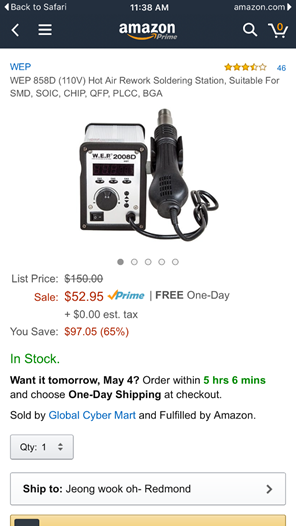

그러한 과정에는 핫 에어건을 사용한 MCU de-soldering 과정을 거칩니다. 특정 온도 (섭씨 350 ~ 400도)로 2분 내의 열을 가하는 정도가 대부분의 경우에 통용되는 정도의 범위입니다.

핫에어 블로어

핫에어 블로어는 다음과 같이 100불 이하의 제품도 많이 구할 수 있고, 시큐리티 리서치 용도로 사용하는데에 있어서 큰 문제 없이 사용 가능합니다.

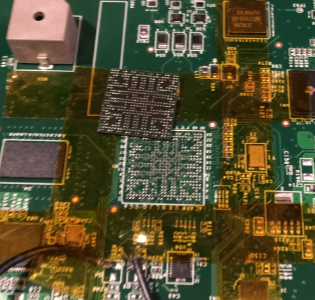

Pins exposed

다음은 de-solering후 노출된 핀들을 보여 줍니다.

이렇게 노출된 위치의 핀들과 기판상의 노출된 위치에 있는 핀들 사이의 연결 지점을 찾는 것이 다음 단계입니다.

이러한 작업은 멀티미터등의 도구를 통해서 가능합니다. 다음번 아티클에서는 멀티 미터등의 기기를 통해서 어떻게 JTAG 포트를 찾고, 실제로 어떠한 도구를 사용해서 JTAG 커넥션을 만들어 기기를 제어할 수 있는지에 대해서 공유하겠습니다.